What is Boundary Scan?

Boundary Scan is an architecture embedded into many modern electronic devices that allows signals to be tested and controlled without physical test probes. This technology uses a chain of cells located inside the chip to read or drive signals through a standard test port.

Boundary Scan is particularly valuable in high-density boards where test access is limited, and it is widely used in:

- Electronic design

- Hardware validation

- Manufacturing and ICT test

- Failure diagnosis and repair

How Does Boundary Scan Work?

Every IEEE 1149.1–compliant component contains a series of small cells called Boundary Scan Cells, located between the chip’s core logic and its external pins. These cells provide direct digital control and observation capability over I/O signals.

These cells allow the system to:

- Capture the value of a signal

- Force a logical value (1 or 0)

- Isolate a pin to test the surrounding circuitry

- Verify connectivity between components

The test operates by shifting a bitstream through the internal scan chain, cell by cell. Once the sequence has propagated across the device, the chip shifts the results back to the test software, where the responses are analyzed to determine whether a fault exists.

What Faults Can Boundary Scan Detect?

Boundary Scan is ideal for structural and interconnect testing, enabling the detection of defects that are often difficult—or even impossible—to find using traditional probing methods. Common detectable failures include:

Structural Faults

- Shorts between pins or traces

- Open circuits

- Bus contention or communication errors

- Lifted or unsoldered pins

- Swapped or misrouted nets

Component-Level Validation

- Device ID readout on JTAG-enabled components

- Verification of DDR, NAND, and eMMC memory devices

- Diagnosis of I²C, SPI, and PMBus sensors and peripherals

- Voltage measurement and monitoring

- Detection of pull-up/pull-down resistor presence

- Connector testing without physical access

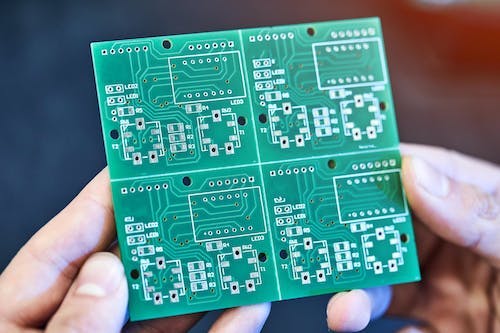

Boundary Scan in ICT: How It Increases Test Coverage

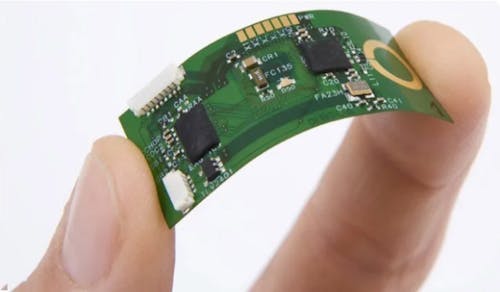

In traditional ICT systems, test coverage relies heavily on physical access to test points. However, modern PCB designs often reduce the number of available pads due to space and cost constraints.

This is where Boundary Scan becomes the perfect complement to ICT.

Standard ICT functions enabled through Boundary Scan include:

- TAP Integrity

- Powered Shorts Testing

- Interconnect Tests

- Bus-wire Tests

- Connect Tests

- Silicon Nails (indirect signal activation)

These capabilities allow manufacturers to significantly increase test coverage without adding fixture complexity or requiring additional physical probing.

Boundary Scan Capabilities by Component Type

Boundary Scan provides valuable flexibility when interacting with multiple component types across a board. Whether working with memory devices, interface controllers, sensors, or power management components, its ability to digitally access and control signals makes it an effective tool for validating functionality and interconnect integrity.

Memory Devices

- DDRx, NAND, eMMC

- Basic pattern testing (non-speed tests)

- Read, write, and verify operations

ADCs and DACs

- Controlled through serial interfaces

- Reading converted values

SPI / I²C

- Temperature sensors

- Power monitors / PMBus

- Port expanders

- Real-Time Clock (RTC)

- SPI Flash

Connectors

- Line verification without physical access

- Continuity and connection testing

Boundary Scan Limitations

Although Boundary Scan is a powerful technology, it does come with certain limitations, such as:

- Not all devices implement JTAG

- Complex components may require advanced BSDL models

- Dual-TAP or multi-core devices can introduce challenges

- Test access may be limited if the design lacks proper DFT planning.

Keysight X1149: A Key Tool for Boundary Scan Testing

The Keysight X1149 Boundary Scan Analyzer is one of the most widely used tools in the industry for implementing JTAG-based testing easily and efficiently—even outside traditional ICT environments.

Key Features

- Intuitive user interface

- Parallel memory testing

- Voltage monitoring capabilities

- Support for IEEE 1149.1, 1149.6, and 1687

- In-system programming for Flash, CPLD, and FPGA

- Seamless integration with ICT 3070 systems

- Faster debugging compared to traditional ICT

Furthermore, the X1149 allows the same HW to be reused across multiple fixtures.

IEEE 1687 (iJTAG): The Next Evolution of the Standard

IEEE 1687 extends JTAG technology by enabling access to internal instrumentation within a chip—such as embedded sensors, monitors, and diagnostic elements. This makes it a critical enabler for modern device architectures, including SoCs and high-density digital systems.

Real-World Results: Increased Speed and Coverage

Practical deployment of Boundary Scan in production environments has shown significant improvements in test efficiency and diagnostic capability. When combined with ICT, this methodology accelerates execution time, increases test coverage, and simplifies validation of complex digital components.

Examples include:

- DDR testing was reduced to one-quarter of the original time

- Complete verification of eMMC devices

- SPI Flash programming without physical access points

- LED activation using Silicon Nails

- Improved coverage between disconnected devices through Scan Chain Linker

Boundary Scan has become an essential resource in the design, testing, and manufacturing of modern electronic assemblies. Its diagnostic capabilities, paired with standards such as IEEE 1149.1 and 1687, unlock levels of test coverage that traditional methods cannot match.

Tools like the Keysight X1149 amplify these advantages—speeding up testing, improving debug efficiency, and enabling smooth integration with existing ICT systems.

Boundary Scan is not just a test technique—it's a strategic foundation for ensuring reliability, quality, and efficiency in today’s electronics production.

If you found this article helpful, you'll be even more interested in hearing the technical explanation directly from the expert.

Presentation available on YouTube — Boundary Scan Innovation with Salvador Galván